[TECHNICAL SESSION - AI / ML APPLICATIONS]

# ULTRA-LOW POWER EDGE AI ASICS

#### **SWAMY IRRINKI**

VP of Marketing and Business Development

@Copyright

www.moschip.com

- AI Edge Devices End Application Examples

- Edge Accelerator/ASICs for Low Power Edge Devices

- Edge Devices AI Chip Market

- MosChip ASIC Platform for Smart Edge Devices

- Edge Implementation Examples /Demo

- Conclusions

- Q&A

# **AI Edge Devices End Application Examples**

AI Self Checkout

AI Facial Recognition

Autonomous Mobile Robots in Manufacturing

# Edge Al Accelerators - Customized for Specific Edge Devices

| Pros and cons        | Processor                                                                                                                                                 |                                                                                                                                                                                                                                                          |                                                                                                                                                       |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                      | СРИ                                                                                                                                                       | GPU                                                                                                                                                                                                                                                      | Edge AI accelerator                                                                                                                                   |  |

| Advantage            | <ul> <li>Easily to implement any algorithms</li> </ul>                                                                                                    | <ul> <li>Can process high throughput<br/>video data</li> <li>High memory bandwidth</li> <li>High parallel processing ability</li> </ul>                                                                                                                  | <ul> <li>Power and computation efficient</li> <li>Compact size</li> <li>Customizable design for the specific application</li> </ul>                   |  |

| Disadvantage         | <ul> <li>The sequential processing fea-<br/>ture does not match the charac-<br/>teristic of CNN, requiring mas-<br/>sively parallel computing.</li> </ul> | <ul> <li>Requires massive power support</li> <li>Restricts its application for<br/>power-sensitive edge devices</li> <li>Images in a streaming video and<br/>some tracking algorithms are in-<br/>putted sequentially but not paral-<br/>lel.</li> </ul> | <ul><li>targeted application (inflexible<br/>for all type computations)</li><li>Computational power limited<br/>compared to data center CPU</li></ul> |  |

| Application platform | <ul> <li>More suitable for datacenter</li> <li>Cooperate with AI accelerator</li> </ul>                                                                   | <ul> <li>More suitable for datacenter</li> <li>Cooperate with AI accelerator</li> </ul>                                                                                                                                                                  | <ul> <li>Customized for specific edge de<br/>vices</li> <li>Can cooperate with CPU or<br/>GPU</li> </ul>                                              |  |

Source: Low-power Ultra-small Edge AI Accelerators for Image Recognition with Convolution Neural Networks: Analysis and Future Directions Weison Lin 1, \*, Adewale Adetomi 1 and Tughrul Arslan 1 Institute for Integrated Micro and Nano Systems, University of Edinburgh, Edinburgh EH9 3FF, UK; adewale.adetomi@ed.ac.uk; tughrul.arslan@ed.ac.uk

#### **INOSCHIP** ASIC- High Performance with Low Power Consumption

| Core<br>Type | Custom<br>ASIC | Typical Power<br>Consumption | Description                                        | Strengths                                                                                                           | Constraints                                                                          |

|--------------|----------------|------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| CPU          |                | High                         | Flexible, general purpose processing units         | <ul> <li>Complex instructions and tasks</li> <li>System management</li> </ul>                                       | <ul> <li>Possible memory access<br/>bottlenecks</li> <li>Few cores (4-16)</li> </ul> |

| GPU          |                | High                         | Parallel cores for high quality graphics rendering | <ul> <li>High performance AI processing</li> <li>Highly parallel core with 100's or<br/>1,000's of cores</li> </ul> | <ul> <li>High power consumption</li> <li>Large footprint</li> </ul>                  |

| FPGA         |                | Medium                       | Configurable logic gates                           | <ul><li>Flexible</li><li>In-field reprogrammability</li></ul>                                                       | <ul><li>High power consumption</li><li>Programming complexity</li></ul>              |

| ASIC         |                | Low                          | Custom logic designed<br>with libraries            | <ul> <li>Fast and low power consumption</li> <li>Small footprint</li> </ul>                                         | <ul><li>Fixed function</li><li>Expensive custom design</li></ul>                     |

Source: https://blog.adlinktech.com/2021/02/19/embedded-hardware-processing-ai-edge-gpu-vpu-fpga-asic

#### **Edge Devices Al Chip Market** ASIC Segment to Record 20.9% CAGR

| Туре         | 2027 TAM   | CAGR  |

|--------------|------------|-------|

| ASIC         | \$1B       | 20.9% |

| CPU/GPU/FPGA | \$4.5B     | 16.7% |

|              | @Convright |       |

@Copyright

## ASICs are Optimized for Ultra-Low Power Sensitive Edge Devices

#### **Cost & Power Sensitive applications**

- Battery Life and Low Cost

- Always-On Sensor hub

- Addressing privacy concerns through On-device AI

- Low-Light Image Processing (RGB-IR) with HDR

## ASIC Development for Ultra-Low Power Edge Devices

ASICs enable high-performance processing with low-power consumption and small form factor, a must for edge devices

ASICs are optimized for a specific application compared to GPU/CPU/FPGAs

ASICs can deliver AI functionality at a lower unit price point (Requires upfront investment)

Most of edge device ASICs can be developed in mature process nodes (22nm/28nm and above)

#### **MOSCHib**

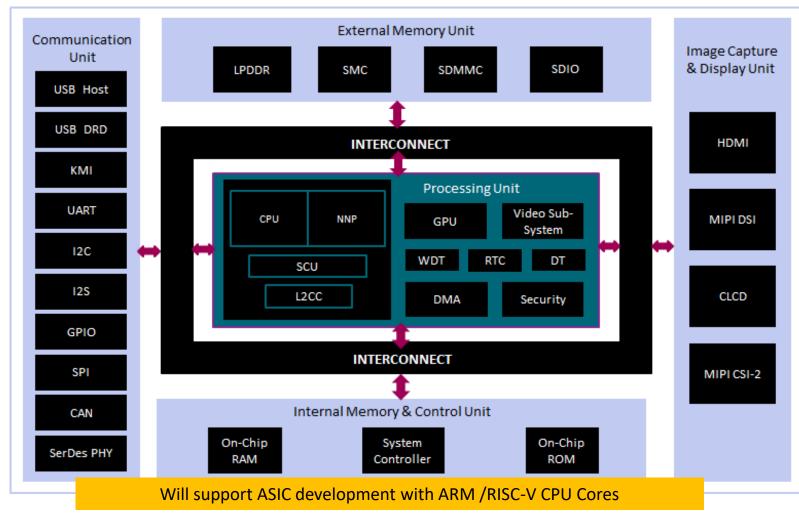

## Matrix I – ASIC Platform for Edge Devices (40nm)

- TSMC 40nm

- Flip Chip

- ARM cortex A9 dual core

- Trust Zone Support for ARM

- GPU- Mali 400

- ARC417 video processor

- USB3.0 Host /OTG Controller

- LPDDR2/DDR3 Controller

- SRAM, NAND, NOR controller

- GNSS

- SDIO, SDMMCC

- CLCD Display Controller

- MIPI DSI Controller

- MIPI CSI II Controller

- Network Interconnect (NIC301)

- 8 Channel DMA

- HDMI 1.4a Rx & HDMI 1.4a Tx

- I2S Controller

- SPI, I2C and UART Controller

- CAN and GPIO Controller

- Keypad/Mouse Controller

- RTC ,WDT, Timer

- iBoot Code Development

- UBoot Porting

- Bare-metal drivers for LCD, MIPI CSI, DSI

- Integration of bare metal drivers for IP's

- Linux OS Porting & required drivers

- System boot time optimisation

- Power Management

- Boot Modes (NOR,SD,SPI-Flash,NAND)

- Bare-metal & Linux based test applications

#### MATRIX II - ASIC PLATFORM FOR ULTRA-LOW POWER SMART EDGE DEVICES (28NM) BRAINCHIP AKIDA NEURAL NETWORK PROCESSOR (NNP) IP

@Copyright

#### **MosChip's Mixed Signal and Analog IP for Edge Devices**

(Matrix II ASIC Platform)

| SerDes PHY                          | Standards             | PCS         | Data Rate per Lane (Gbps)         | Features                                                                                    |  |

|-------------------------------------|-----------------------|-------------|-----------------------------------|---------------------------------------------------------------------------------------------|--|

| PCle Gen 1                          | PCle 1.1              | PIPE        | 2.5                               | Endpoint or Root Complex PIPE includes skip insertion,<br>deletion PCIe power savings modes |  |

| PCle Gen 2                          | PCle 1.1              | PIPE        | 2.5                               | Endpoint or Root Complex PIPE includes skip insertion,                                      |  |

|                                     | PCle 2.0              | PIPE        | 5.0                               | deletion PCIe power savings modes<br>Port bifurcation support                               |  |

| XAUI                                | XAUI, CX4, KX4        | Customer    | 2.4 - 3.2 / 1.2 - 1.6             | Generic backplane uses                                                                      |  |

| CEI-6                               | CEI-6, XAUI, CX4, KX4 | Customer    | 4.8 - 6.4 / 2.4 - 3.2 / 1.2 - 1.6 | Generic backplane uses                                                                      |  |

| SATA I/II -                         | SATA I                | SATA        | 1.5                               | Advanced frequency offset (PPM) compensation                                                |  |

|                                     | SATA II               | SATA        | 3.0                               | for +0 / -0.5% SSC                                                                          |  |

| Switchable                          | Multiple              | Multiple    | Multiple                          | Switchable between 2 or 3 standards<br>Separate interface for each standard                 |  |

| ARM HSSTP                           | HSSTP 6.0             | Aurora Link | 6.25 / 12.5                       | ARM HSSTP PHY along with Link Layer as a single macro                                       |  |

| PCle Gen 3                          | PCle 3.0              | Partners    | 8                                 | Backward compatible to Gen2 and Gen1                                                        |  |

| PCle Gen 4                          | PCle 4.0              | Partners    | 16                                | Backward compatible to Gen3, Gen2 and Gen1                                                  |  |

| Chip2Chip                           |                       | Customer    | 10                                | Supports USR (6 dB), VSR(9 dB) and SR(15 dB)                                                |  |

| SerialLite                          | IEEE149.1             | PCS         | 3.125                             | chip2chip, board2board, shelf2shelf or backplane                                            |  |

| Analog IP - ADC/DAC, LVDS I/O, PLLs |                       |             |                                   |                                                                                             |  |

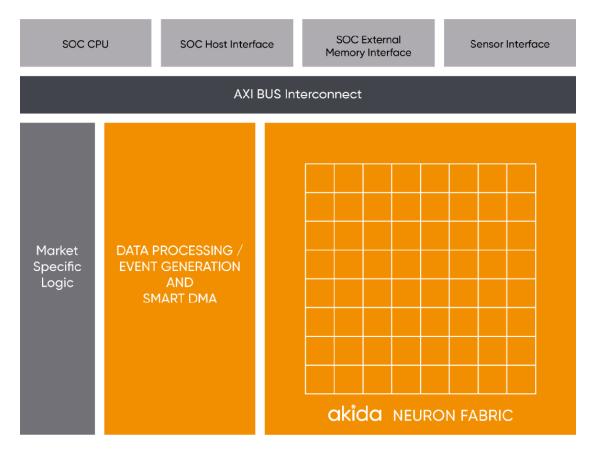

# BrainChip's NNP IP Akida is Uniquely Essential *For Ultra-Low Power Edge Devices*

- BrainChip's IP fabric can be placed either in a parallelized manner that would be ideal for ultimate performance, or space-optimized in order to reduce silicon utilization and further reduce power consumption.

- Entire neural networks can be placed into the fabric, removing the need to swap weights in and out of DRAM resulting in a reduction of power consumption while increasing throughput.

- Additionally, users can modify clock frequency to optimize performance and power consumption further.

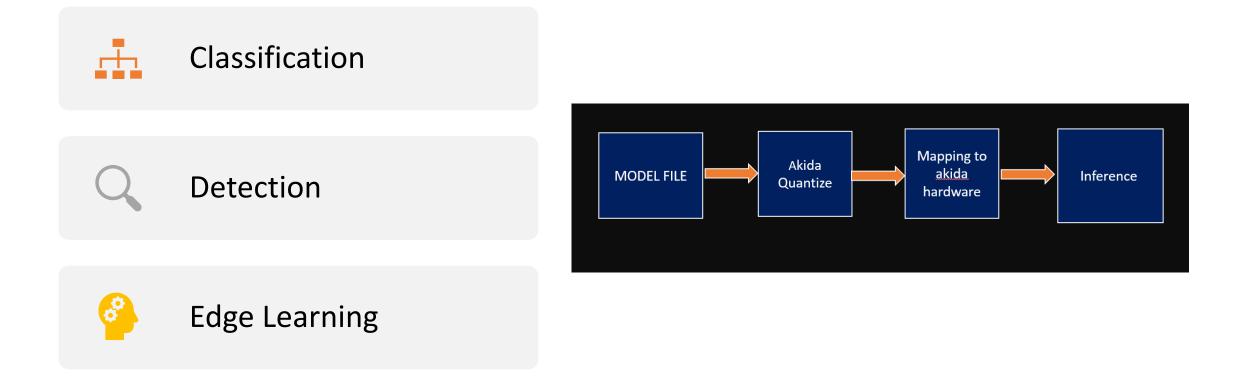

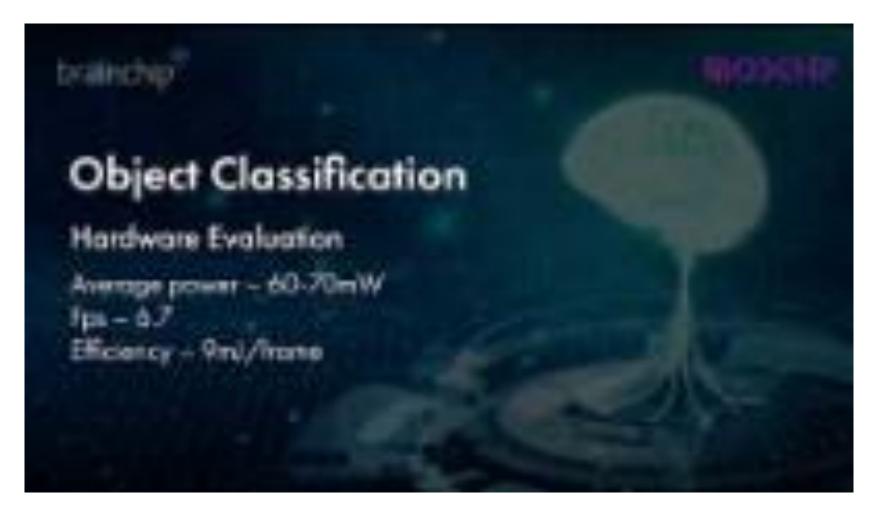

# **Akida IP Edge Implementation Examples**

### Demo

14

# Conclusions

Edge AI Accelerators can be customized for specific edge device/application

ASICs enable high-performance processing with low-power consumption and small form factor

MosChip ASIC Platform with Brainchip's Akida NNP IP will enable customers to develop and bring-up custom SoC solutions for ultra-low power smart edge devices

www.moschip.com

0

@Copyright